GPIO Pins: Behind the Scenes

GPIO (General Purpose Input/Output) pins are essential components of microcontrollers that enable seamless interaction between the microcontroller and the external world. Their ability to function as either inputs or outputs allows for versatile control of external devices and sensors. However, beneath this apparent simplicity lies a fascinating realm of buffer logic and intricate circuitry that enables these tiny yet powerful elements to operate efficiently and reliably. In this article, we will explore the concepts of buffer logic, unravel the inner workings of GPIO pins, and understand how the enable line influences their behavior. Additionally, we will delve into how special pins like UART, I2C, and ADC play a vital role in enabling advanced functionalities in embedded systems.

Understanding GPIO Pins and Buffer Logic

GPIO pins serve as a fundamental part of microcontrollers, facilitating bidirectional communication between the microcontroller and external devices. They allow the microcontroller to send signals (output mode) or receive signals (input mode) to control or gather data from various peripherals, sensors, and actuators. Each GPIO pin possesses configurable registers and internal circuitry that dictate its behavior.

GPIO Configuration

At the core of GPIO functionality lies the concept of buffer logic. Each GPIO pin is associated with buffers, which acts as an intermediary between the microcontroller’s internal circuitry and the external world. The buffer can be controlled by setting specific registers in the microcontroller.

There is one input buffer, one output buffer, and an enable line. When an enable line is zero, the output buffer gets activated, and the input buffer gets deactivated.

Buffer

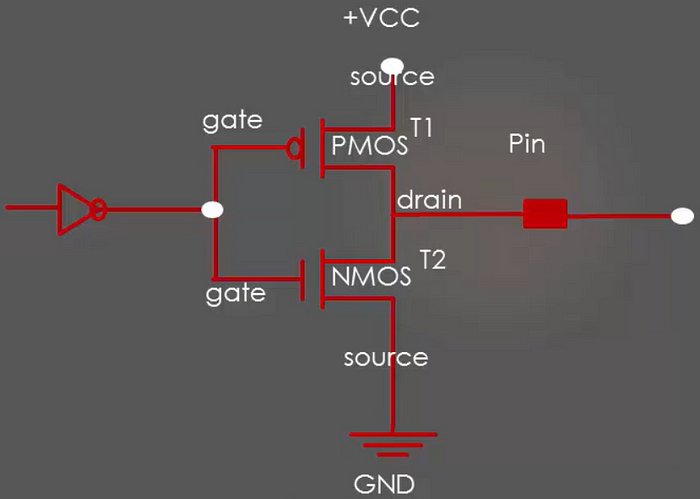

The top transistor in the buffer is called a PMOS transistor, and the bottom one is called an NMOS transistor. Understanding the operation of these transistors is crucial to comprehend the behavior of GPIO pins.

Buffer Logic: Output Mode

In output mode, the GPIO pin can drive an external device with a digital signal. When writing a logic 1 to the output pin, the PMOS transistor (T1) gets activated, allowing the current to flow from the supply voltage (Vcc) to the pin. At the same time, the NMOS transistor (T2) is deactivated, preventing any current flow to ground. As a result, the output pin provides a logic 1. Conversely, when writing a logic 0, the NMOS transistor (T2) gets activated, pulling the output pin to ground (GND), while the PMOS transistor (T1) is deactivated. This results in a logic 0 being output onto the pin. In this way, the output buffer of a GPIO pin controls the logic level that is driven onto the pin.

Buffer Logic: Input Mode

In input mode, the GPIO pin reads the voltage level from an external device. When the enable line is set to one, the pin is configured as an input. In this state, the PMOS transistor (T1) is turned on, while the NMOS transistor (T2) is turned off. If the external device applies a higher voltage, the PMOS transistor (T1) remains on, and the pin is read as logic high. On the other hand, if the external device applies a lower voltage, the PMOS transistor (T1) turns off, and the NMOS transistor (T2) conducts, pulling the pin to ground, which results in a logic low being read at the pin.

Buffer Enable and Disable

To prevent accidental damage to the microcontroller or external devices, an additional register called the “GPIO Enable Register” (or similar) is provided. This register allows the programmer to enable or disable the buffer for each GPIO pin.

- When the buffer is enabled (enable line = 1), the GPIO pin operates in either input or output mode, as per its configuration. The buffer actively drives the pin’s output or reads the input voltage level from the external device.

- When the buffer is disabled (enable line = 0), the GPIO pin enters a high-impedance state (Hi-Z), effectively disconnecting it from the external circuitry. In this state, the GPIO pin does not drive any output or draw any current from the external device, making it safe to connect the pin to other devices without interference.

The ability to enable and disable the buffer on a GPIO pin provides control over the pin’s behavior and ensures safe operation in various application scenarios.

UART (Universal Asynchronous Receiver/Transmitter) Pins

UART pins, also known as serial communication pins, are critical for inter-device communication. UART employs two GPIO pins: one for transmission (TX) and one for reception (RX). The UART protocol uses asynchronous communication, where data is transmitted without a shared clock signal between the sender and receiver.

- TX Pin: The microcontroller’s UART transmitter sends serial data as a stream of bits via the TX pin. Buffer logic amplifies and formats the data before sending it to an external device. When the UART is enabled for transmission, the buffer drives the TX pin to produce the serial data stream.

- RX Pin: The UART receiver, connected to the RX pin, reads incoming serial data. Buffer logic detects the voltage levels at the pin, converting the received bits into a data stream for processing within the microcontroller. When the UART is enabled for reception, the buffer reads the voltage levels at the RX pin to reconstruct the incoming serial data.

I2C (Inter-Integrated Circuit) Pins

I2C is a popular communication protocol for connecting multiple devices on the same bus. It uses two GPIO pins: one for data (SDA) and one for the clock (SCL). I2C employs a master-slave architecture, where the microcontroller acts as the master and controls the communication with one or more slave devices.

- SDA Pin: The SDA pin handles bidirectional data communication between the master and slave devices. Buffer logic is designed to drive the pin during data transmission and read data from the pin during reception. When the master microcontroller wants to send data, the buffer drives the SDA pin with the appropriate data bits. During reception, the buffer reads the voltage levels at the SDA pin to obtain the data sent by the slave devices.

- SCL Pin: The SCL pin serves as the clock signal for synchronizing data transfer. Buffer logic generates the clock pulses on this pin, ensuring synchronized communication between devices. When the master microcontroller sends or receives data, the buffer controls the timing of the clock pulses on the SCL pin.

ADC (Analog-to-Digital Converter) Pin

Unlike GPIO, UART, or I2C, ADC pins are dedicated to converting analog signals into digital data. These pins allow microcontrollers to interface with sensors and other analog devices.

- ADC Pin: The ADC pin, often labeled as an analog input, receives an analog voltage from an external sensor. Buffer logic conditions the analog voltage, and the analog-to-digital converter within the microcontroller samples and converts it into a digital value for further processing. During ADC conversion, the buffer ensures that the voltage at the ADC pin remains stable and unaffected by internal circuitry.

Conclusion

GPIO pins, powered by buffer logic, form the backbone of microcontroller-based systems, enabling communication and control of external devices. Special pins like UART, I2C, and ADC add versatility and advanced capabilities to embedded systems. Understanding the intricacies of buffer logic and the unique functionalities of these special pins empowers electrical engineers to create innovative and reliable designs that drive technology forward. Embrace the magic of GPIO pins and explore the possibilities of UART, I2C, and ADC to craft the next generation of intelligent devices. With this knowledge, you can unlock the full potential of microcontrollers and create cutting-edge solutions that shape the future of technology.